CASE STUDIES

Three large capacity, high speed nonvolatile SRAM contrast

Three large capacity, high speed nonvolatile SRAM contrast

In embedded systems, the use most non-volatile memory block is the EEPROM and FLASH (Non - Volatile), is mainly used to save the program or data, but the two have a common memory defect is slow to write, write algorithm is more complex, and cannot meet th

Show Detail >>

Introducing Bluetooth mesh networking

Introducing Bluetooth mesh networking

Bluetooth mesh capability enables many-to-many device communications in large-scale device networks for building automation sensor networks and other IoT solutions

Show Detail >>

Robots Get AI from Startup

Robots Get AI from Startup

Startup Embodied Intelligence announced software to embed machine-learning capabilities into industrial robots

Show Detail >>

NXP to Bridge MCU & AP with 'Crossovers'

NXP to Bridge MCU & AP with 'Crossovers'

To use an MCU or not (and to opt for an apps processor instead)? This is an eternal question for embedded system designers, and one that NXP Semiconductors hopes to answer by launching a new high-end MCU

Show Detail >>

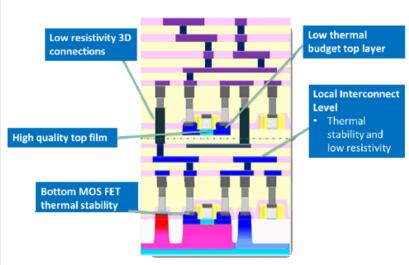

Monolithic 3D: Promise, Challenges

Monolithic 3D: Promise, Challenges

Researchers said monolithic 3D chip stacks have promise but face several challenges at an event attended by CEA-Leti, Qualcomm, ARM and others

Show Detail >>

DRAM Capacity Crunch Expected to Persist in 2018

DRAM Capacity Crunch Expected to Persist in 2018

With suppliers planning only limited capacity and demand on the rise, DRAMeXchange says price declines unlikely

Show Detail >>

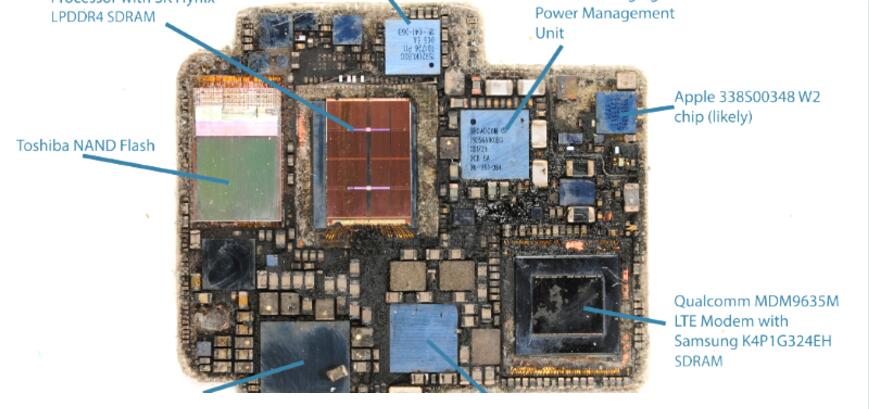

Apple Watch Packs Qualcomm LTE

Apple Watch Packs Qualcomm LTE

Qualcomm supplied the LTE modem in the Apple Watch Series 3 as well as a handful of other wireless chips, acco

Show Detail >>

Win some, lose some: DRAM stands on shaky ground

Win some, lose some: DRAM stands on shaky ground

DRAM has found itself in the situation of being a low-margin, commodity memory in a slowing tablet and PC market, while it still makes the most sense from a performance, density and cost perspective

Show Detail >>CONTACT US

Zarchin 10St.Raanana,43662 Israel

238884 Singapore