3D semicircular Flash memory cell structure increases density

KIOXIA has developed the world’s first 3D semicircular split-gate flash memory cell structure with specially designed semicircular Floating Gate (FG) cells.

Twin BiCS FLASH offers better program slope and a larger program/erase window at a smaller cell size compared to circular Charge Trap (CT) cells. These attributes make this new cell design a promising candidate to surpass four bits per cell (QLC) for significantly higher memory density and fewer stacking layers.

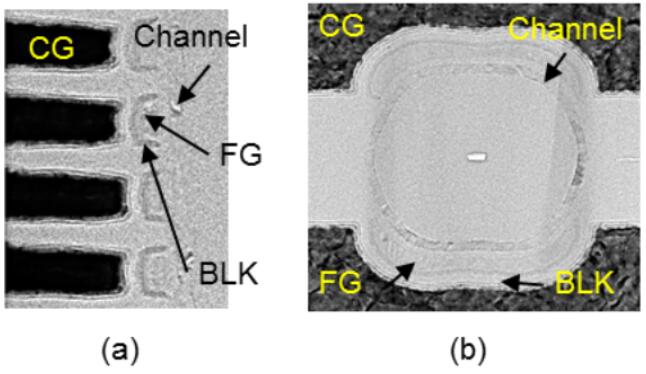

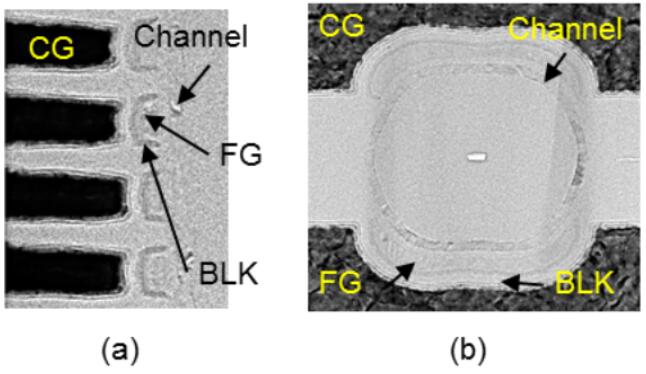

3D flash memory technology achieves high bit density and low cost per bit through increasing the number of cell stacked layers and implementing multilayer stack deposition and high aspect ratio etching. Recently the number of cell layers has exceeded 100, making managing the trade-offs among etch profile control, size uniformity and productivity increasingly challenging. KIOXIA’s new semicircular cell design splits the gate electrode in the conventional circular cell to reduce cell size compared to the conventional circular cell, enabling higher-density memory at a lower number of cell layers.

The circular control gate offers a larger program window with relaxed saturation problems when compared with a planar gate because of the curvature effect, where carrier injection through the tunnel dielectric is enhanced while electron leakage to the block (BLK) dielectric is lowered. In the split-gate cell design, the circular control gate is symmetrically divided into two semicircular gates, taking advantage of the improvement in the program/erase dynamics. The conductive storage layer is used for high charge trapping efficiency in conjunction with the high-k BLK dielectrics, achieving high coupling ratio to gain program window as well as reduced electron leakage from the FG, relieving the saturation issue. The experimental program/erase characteristics reveal that the semicircular FG cells with the high-k-based BLK exhibit significant gains in the program slope and program/erase window over the larger-sized circular CT cells. The semicircular FG cells, having superior program/erase characteristics, are expected to attain comparably tight QLC Vt distributions at small cell size. Further, integration of low-trap Si channel makes possible more than four bits/cell, e.g., Penta-Level Cell (PLC). These results confirm that semicircular FG cells are a viable option to pursue higher bit density.

Twin BiCS FLASH offers better program slope and a larger program/erase window at a smaller cell size compared to circular Charge Trap (CT) cells. These attributes make this new cell design a promising candidate to surpass four bits per cell (QLC) for significantly higher memory density and fewer stacking layers.

3D flash memory technology achieves high bit density and low cost per bit through increasing the number of cell stacked layers and implementing multilayer stack deposition and high aspect ratio etching. Recently the number of cell layers has exceeded 100, making managing the trade-offs among etch profile control, size uniformity and productivity increasingly challenging. KIOXIA’s new semicircular cell design splits the gate electrode in the conventional circular cell to reduce cell size compared to the conventional circular cell, enabling higher-density memory at a lower number of cell layers.

The circular control gate offers a larger program window with relaxed saturation problems when compared with a planar gate because of the curvature effect, where carrier injection through the tunnel dielectric is enhanced while electron leakage to the block (BLK) dielectric is lowered. In the split-gate cell design, the circular control gate is symmetrically divided into two semicircular gates, taking advantage of the improvement in the program/erase dynamics. The conductive storage layer is used for high charge trapping efficiency in conjunction with the high-k BLK dielectrics, achieving high coupling ratio to gain program window as well as reduced electron leakage from the FG, relieving the saturation issue. The experimental program/erase characteristics reveal that the semicircular FG cells with the high-k-based BLK exhibit significant gains in the program slope and program/erase window over the larger-sized circular CT cells. The semicircular FG cells, having superior program/erase characteristics, are expected to attain comparably tight QLC Vt distributions at small cell size. Further, integration of low-trap Si channel makes possible more than four bits/cell, e.g., Penta-Level Cell (PLC). These results confirm that semicircular FG cells are a viable option to pursue higher bit density.

CONTACT US

USA

Vilsion Technology Inc.

36S 18th AVE Suite A,Brington,Colorado 80601,

United States

E-mail:sales@vilsion.com

Europe

Memeler Strasse 30 Haan,D 42781Germany

E-mail:sales@vilsion.com

Middle Eastern

Zarchin 10St.Raanana,43662 Israel

Zarchin 10St.Raanana,43662 Israel

E-mail:peter@vilsion.com

African

65 Oude Kaap, Estates Cnr, Elm & Poplar Streets

Dowerglen,1609 South Africa

E-mail:amy@vilsion.com

Asian

583 Orchard Road, #19-01 Forum,Singapore,

238884 Singapore

238884 Singapore

E-mail:steven@vilsion.com