Why FPGAs are good fit for industrial applications

Product developers who are concerned about functional safety want to develop their products so that they meet standards and performance requirements that are created to protect against potential risks. The challenge for designers is that the functional safety specification is about risk mitigation; the idea is to remove risk until the product reaches a determined level of safety. There are many ways of achieving the desires result, such as using dual-core lock-step for processors, ECC protection for memory or some form of custom safety implementation logic. To facilitate building functionally safe designs, robust synthesis tools that support defined methods are needed, such as Synplify Premier, which provides FPGA designers with technologies that facilitate including functional safety capabilities into their products.

If we look at motor control, for example, there are an increasing number of FPGAs driving these types of systems that are integrating functional safety. An FPGA is comprised of building blocks that include logic, BRAMs, registers, DSPs, digital clock generators and input and output buffers, all of which need to be considered when designers implement critical portions of the design using these functions.

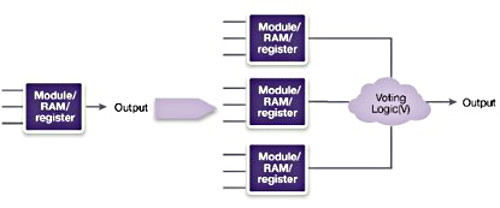

There are many techniques that can be applied to protect the various FPGA blocks forming the design, but implementing these techniques by hand is time-consuming and prone to error. Designers need a set of tools that allow them to automate the protection of these blocks by implementing techniques that can detect the presence of an error and correct or mitigate the issue. For example, tools that support design automation for such things as ECC RAM instantiation, safe finite state machines (FSMs), triplication of the design (or selected portions thereof) to implement triple-modular redundancy (TMR) and memory scrubbing, all of which help mitigate the risk of potential harm to people.

Figure 1: Automatic triplication of logic, RAM, or register with voter logic on output (Source: Synopsys)

Figure 1: Automatic triplication of logic, RAM, or register with voter logic on output (Source: Synopsys)

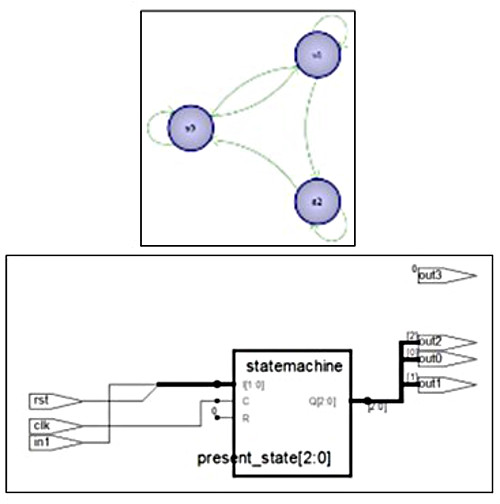

We may also need to protect higher-level macros, like FSMs and IP blocks, which can present challenges, such as in circuits that contain synchronous feedback. There are several techniques that can be applied to detect and correct errors in FSMs, including methods for creating safe-state machines or for performing Hamming-3 error detection and correction.

Figure 2: Finite state machine (FSM) diagram and schematic (Source: Synopsys)

Figure 2: Finite state machine (FSM) diagram and schematic (Source: Synopsys)

For industrial applications, the overall average lifetime of manufacturing equipment is growing and designers need to utilise and deploy components that will work reliably for decades. The automated methodologies and single design flow offered by tools like Synplify Premier provides designers with the ability to quickly integrate functional safety into FPGA-based designs and also port their design across multiple FPGA device technologies as required. Depending on the complexity of the design, teams may save hours or even weeks of design implementation time as compared to implementing error detection and mitigation by hand.

CONTACT US

Zarchin 10St.Raanana,43662 Israel

238884 Singapore